MMU-6829

Inhaltsverzeichnis

Motorola MMU 6829

Für die Motorola 6809 gibt es einen perfekt passenden Speicher Manager, die Motorola MMU 6829.

Eine MMU verwaltet den Verfügbaren Arbeitsspeicher eines Computer System. Im Falle einer 8 Bit CPU, die einen sehr eingeschränkten Adressraum hat, wird durch den Einsatz einer MMU der Adressraum stark erweitert.

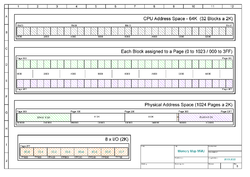

Der Adressraum einer Motorola 6809 CPU ist auf 64K beschränkt, man spricht vom logischen Adressraum.

Die MMU hingegen hat einen viel größeren Adressraum von mehreren MB, das bezeichnet man als physischen Adressraum.

Die Idee hinter der MMU ist es, den logischen Adressraum der CPU in kleine Blöcke zu teilen. Jeder Block kann dann irgendwo im physischen Adressraum verschoben werden. Damit steht der gesamte physikalische Adressraum im Zugriff der CPU, natürlich nur Stückweise.

Je kleiner die Größe eines Blocks gewählt wird, desto flexibler kann die Sicht auf den physikalische Adressraum gestaltet werden. Allerdings vergrößert sich der Verwaltungsaufwand, je kleiner die Blockgröße gewählt wird.

Jeder Speicherzugriff der CPU ist immer ein Zugriff in den logischen Adressraum (64K).

Die MMU rechnet jeden Speicherzugriff um, von der logischen Adresse zur physikalischen Adresse.

Die Umsetzung von logischer auf physikalischer Adresse erfolgt durch ein sehr schnelles RAM, das 'Mapping RAM' (MRAM).

Das ist insbesondere bei einer 3MHz CPU eine ziemliche Herausforderung.

Funktion der MMU

Die CPU 6809 hat einen logischen Adressraum von 64KB (16 Bit). Der logische Adressraum ist unterteilt in 32 Blöcke von je 2K.

Die MMU 6829 hat einen physikalischen Adressraum von 2MB (21 Bit). Der physikalische Adressraum ist in 1024 Seiten (Pages) zu je 2K (Page $000 bis $3FF) unterteilt.

Aus Sicht der CPU kann jeder Block im physischen Adressraum verschoben werden (in 2KB Schritten), wodurch eine hohe Flexibilität erreicht wird. Dazu hat die MMU 32 Zeiger auf je eine Seite im physikalischen Adressraum, die 'Zeiger' sind die Seitennummer. Es erfolgt also eine Zuordnung von Block zu Seite, 32 Blöcke die einem der 1024 Seiten zugeordnet sind.

Die MMU setzt eine Adresse im logischen Adressraum der CPU um in eine Adresse im physikalischen Adressraum.

Die MMU erweitert den Adressraum von einer 16 Bit Adresse zu einer 21 Bit Adresse.

Dazu werden die obersten 5 Bit der logischen Adresse (LA11 bis LA15) erweitert auf 10 Bit (PA11 bis PA20). Diese Erweiterung des Adressraum erfolgt über ein sehr schnelles RAM, dem Mapping RAM (MRAM).

Die obersten 5 Bit der logischen Adresse (LA11 bis LA15) dienen als Adresse für das Mapping RAM (RA0 bis RA4). Das Mapping RAM hat eine Datenbreite von 10 Bit. Die 10 Datenbit des Mapping RAM bilden die obersten Bits der physischen Adresse (PA11 bis PA20).

Das Mapping RAM setzt die logische Adresse um in eine physikalische Adresse.

Damit das Mapping funktioniert, muss man das Mapping RAM beschreiben mit sinnvollem Inhalt.

Dazu wird das Mapping RAM alternativ auch als Speicher im logischen Adressraum eingeblendet.

Der logische Adressraum besteht aus 32 Blöcke (5 Bit). Für jeden Block speichert das Mapping RAM einen 10 Bit Wert (2 Bytes). Das Mapping für den gesamten logischen Adressraum wird als Memory MAP bezeichnet. Aus Sicht der CPU sind das 64 Bytes (32 * 2) für eine MAP.

Die MMU 6829 kann 4 MAPs speichern, das MRAM in der MMU hat also 256 Bytes (4 * 64). Von den 4 MAPs ist immer nur eine MAP aktiv. Die aktive MAP kann man einstellen über ein Register in der MMU 6829. Jeder Task hat seine eigene Memory MAP.

Mit einer MMU 6829 kann man einfach umschalten zwischen 4 Tasks. Ein Task Wechsel ist sehr effektiv, weil man nur die aktive MAP einstellen muss. Der Taskwechsel ist also nur ein einzelner Schreibzugriff (ein Byte).

Wenn man mehr als 4 aktive Tasks hat, dann muss man das MRAM beschreiben bei einem Taskwechsel. Dazu muss man dann 64 Bytes (eine MAP im MRAM) schreiben. Um eine effektive Verwaltung von als 4 Tasks zu haben, kann man mehrere MMU 6829 kaskadieren.

Kaskadierung

Wenn das Multitasking intensiv genutzt wird, dann reichen diese 4 Tasks der MMU nicht mehr aus. In diesem Fall muss das NitrOS9 auf virtuelle Memory MAPs ausweichen. Das bedeutet aber, dass der Task Wechsel jedes mal 64 Bytes kopieren muss. Das bremst das System natürlich aus, darum ist eine größere Anzahl an echten Tasks wünschenswert.

Mit einer MMU hat man 4 'echte' Tasks

- 0: System,

- 1: DMA

- 2,3: User Tasks

Die MMU MC6829 kann sehr einfach kaskadiert werden. Es können bis zu 8 MMUs (32 Tasks) problemlos im selben System arbeiten. Kaskadierte MMU's haben alle Pins bis auf einen einfach durchverbunden. Der eine Pin der unterschiedlich verdrahtet ist, selektiert die gewünschte MMU. Diese Selektion kann zB. durch einen 74LS138 erfolgen.

Verwendung der MMU 6829 im NitrOS9-Board

Die MMU-16 läuft in einem SBC (Single Board Computer), dem NitrOS9-Board.

Memory MAP

Inbetriebnahme

Das Betriebssystem

Das einzige Betriebssystem, das eine MMU unterstützt, ist OS9 ab Level 2. Daher habe ich NitrOS9 Level 2 angepasst für mein NitrOS9 Board mit MMU 6829. Die Basis dafür ist der Quellcode des NitrOS9 für den großartigen Positron 9000 Computer.

Reset Modus

Durch einen Hardware Reset wird in der MMU das Reset Bit gesetzt. Die MMU ist dann in einem speziellen Modus: Reset Modus

Das Reset Bit ist notwendig, weil das Mapping RAM nach dem einschalten einen nicht definierten Inhalt hat. Dadurch wäre das ganze System in einem undefinierten Zustand und könnte nicht richtig gestartet werden.

Zusammenfassung Reset Bit:

- das Reset Signal setzt das Reset Bit, die MMU ist im Reset Modus

- im Reset Modus ist das Mapping RAM inaktiv, alle physikalischen Adressleitungen sind high

- im Reset Modus kann das Mapping RAM beschrieben werden, wie im SU Modus

- das Reset Bit wird zurück gesetzt, sobald man da OP-Key Register beschreibt

System Modus

Durch einen Interrupt (Hardware oder Software Interrupt) wird in der MMU das System Bit gesetzt. Die MMU wechselt dadurch automatisch in den System Modus (oder auch Super User Modus). Solange das System Bit gesetzt ist, ist die MMU immer Task# 0 (System Task). Die Memory Map ist die System Map und die MMU Register sind im Zugriff. Normalerweise wird nun Betriebssystem Code ausgeführt. Das System Bit wird zurückgesetzt, indem man einen Task Wechsel zu einem Benutzer Task durchführt.

Zusammenfassung System Bit:

- ein Interrupt setzt das System Bit, die MMU wechselt in den System Modus

- im System Modus ist immer der Task# 0 (System Task) aktiv

- im System Modus ist die System Memory Map aktiv

- im System Modus ist hat man Zugriff auf die MMU Register und das Mapping RAM

- das System Bit wird zurück gesetzt, sobald man das FUSE Register beschreibt und der FUSE Counter null erreicht

Benutzer Modus

Der Benutzermodus ist quasi der 'Normalbetrieb'. Die CPU führt einen Benutzer Task aus und ist auf die eingestellte Memory MAP beschränkt. Die MMU Register und das Mapping RAM sind nicht im Zugriff, ja sogar vollkommen unsichtbar. Der MMU Speicherbereich ist komplett nutzbar durch die eingestellte Page.

Im Benutzermodus kann das OS aufgerufen werden durch einen Software Interrupt (SWI Befehl).

Hardware Interrupts werden durch das OS bedient. Es funktioniert im Prinzip genau wie ein Taskwechsel.

DMA Zugriffe funktionieren auch ohne Hilfe des OS. Während eines DMA Zugriff wechselt die MMU automatisch in den Task# 1. Die externe Hardware 'sieht' die Memory MAP der Task# 1 die durch das OS konfiguriert wurde.

Start Sequenz

Nach einem Reset fetched die CPU den RESET Vektor von der logischen Adresse $FFFE und führt den Code aus. Die MMU ist nach einem System RESET im Reset Modus. Die Adressleitungen PA11 bis PA23 sind high, daher wird der Reset Vektor gelesen von der physischen Adresse $FFFFFE in der obersten Page (Page 8191). Es läuft privilegierter Code, die MMU Konfig Register sind sichtbar an der Adresse $FF00 bis $FF7F.

Das erste was die CPU nun zu tun hat, ist die Konfiguration der MMU. Sonst hat man keinen Zugriff außerhalb der Page 8191. Die MMU bekommt nun die Konfiguration unter der NitrOS9 laufen kann. Dann wird der Kern Code gestartet. Je nach Art des NitrOS9 ist entweder das gesamte OS im ROM (20K) oder nur der Kern (4K).

Konfiguration der MMU nach einem Reset:

- der Access Key ($FF4A) wird auf Task# 0 gestellt

- das Mapping RAM für Task# 0 wird beschrieben ($FF00 bis $FF3F)

- das Key Value Register KV-0 ($FF40) wird beschrieben, das beende den Reset Modus und aktiviert das Mapping

- nun kann die Kontrolle dem OS übergeben werden

News

- 09.06.2022 --

Downloads