FPGA/HSEDA/XC6SLX16

< FPGA

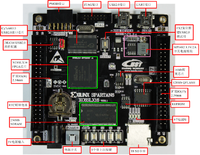

HSEDA Spartan-6 Board

Dieses preisgünstige FPGA Entwicklerboard bietet eine umfangreiche Hardware und ist sehr flexibel einsetzbar. Als FPGA dient ein XILINX Spartan-6 (XC6SLX16). Zusätzlich sind auf diesem Board folgende Ressourcen vorhanden: ein 16-bit SDRAM mit 256 Mb, ein 16 Mb FLASH, ein 128 Mb QFLASH, ein 4Kb EEPROM, ein Echtzeit Uhrenchip, ein USB zu UART interface, ein USB2.0 interface, 5 Taster, 4 bit LCD Display und ein PMOD Interface. Der FPGA hat 84 freie IO Pins die zu den Anschlüssen J6, J7 und J1 führen.

Core Board Ressourcen

- FPGA: XILINX Spartan-6

- SDRAM (256 Mbit)

- FLASH Speicher (16 MB)

- QFLASH (128 MB)

- EEPROM (4 KB)

- RS232 Interface

- LCD interface

- RTC - Echtzeit Uhr

- USB2.0 Kommunikation

- Maße: 8,5 * 8,2 cm

Optionale Schnittstellen

- high-speed Audio Ein- und Ausgangs Karte

- Video Ein- und Ausgangs Karte

- AD-DA Karten

- Gigabit Netzwerk Modul

Spezifikation

- FPGA chip: XC6SLX16-2FTG256C (FBGA256), Speed grade 2, 14579 Logic Elements

- 16 MB × 16 Bit SDRAM (lesen/schreiben 166 MHz)

- FLASH für Konfiguration: M25P16 (16 Mbit)

- 128 Mbit Quad-SPI FLASH (W25Q128)

- EEPROM 4 Kbit (2*256 * 8bit) - (24LC04)

- SD Karten Slot

- USB zu seriell chip (PL2302)

- USB2.0 controller chip (Cypress CY7C68013A)

- Clock 50 MHz (IFCLK 68013)

- RTC chip (DS1302)

- Taster

- Spannungsregler: 5 V, 3,3 V/2A, 1,2 V/800MA

- JTAG Port - 2*7 14PIN 2,0 MM

- LVDS Interface - 8 Paare

- LED: 4 auf freie IO, 2 für RXD/TXT Status

- Reset Taste

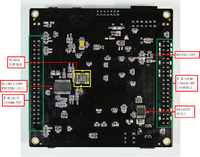

- PCB Layout: 4 fach Layer, Größe: 85mm X 82mm

- PMOD interface

- I/O Schnittstelle: 84 unabhängige IO

- (J6) 38 IO

- (J7) 38 IO

- (J1) 8

An den Schnittstellen J6 und J7 können Erweiterungsmodule angesteckt werden. Der J1 ist ein XILINX PMOD standard Interface.

Dokumentation