FPGA/Alchitry/Au: Unterschied zwischen den Versionen

Tw (Diskussion | Beiträge) (→Alchitry Au) |

Tw (Diskussion | Beiträge) (→WEB Links) |

||

| Zeile 35: | Zeile 35: | ||

=== WEB Links === | === WEB Links === | ||

| − | * [https://alchitry.com/blogs/tutorials/getting-started-with-the-au Einführung] | + | * [https://alchitry.com/blogs/tutorials/getting-started-with-the-au Einführung in das AU] |

| + | * [https://alchitry.com/pages/lucid-fpga-tutorials Einführung in LUCID] | ||

| + | * [https://alchitry.com/pages/verilog-fpga-tutorials Einführung in Verilog] | ||

* [[Media:Alchitry_au_sch.pdf|Schaltbild des Alchitry AU]] | * [[Media:Alchitry_au_sch.pdf|Schaltbild des Alchitry AU]] | ||

* [[Media:Alchitry_elements.zip|Element Eagle Library]] | * [[Media:Alchitry_elements.zip|Element Eagle Library]] | ||

Version vom 22. September 2019, 17:29 Uhr

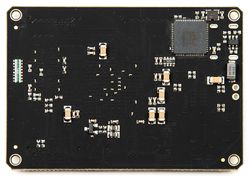

Alchitry Gold (AU)

Das Alchitry Au ist der Nachfolger des Mojo v3 und eignet sich hervorragend als Einsteiger Board in die Welt der FPGA.

Das Ziel bei der Entwicklung des Alchitry Board ist eine einfache Benutzung. Alles ist darauf ausgelegt, einen möglichst einfachen Einstieg zu bekommen in die Entwicklung von digitalem Design mit einem FPGA. Zu diesem Board gibt es eine gute Anleitung und viele praktische Beispiele, die den Einstieg erleichtern und das Wissen über digitales Design erweitern.

Für den Alchitry gibt es eine eigene IDE die sehr Bediener freundlich ist. Wie bei einem Arduino braucht es nur einen Klick, um den Sourcecode zu kompilieren und in das Alchitry Board hoch zu laden.

Erwähnenswert ist auch die neue Sprache Lucid, die der Erfinder des Mojo entwickelt hat. Lucid basiert auf Verilog und abstrahiert die für Anfänger verwirrende Schreibweise in den üblichen Sprachen Verilog und VHDL.

Spezifikation

Das Au ist das leistungsfähigste FPGA Entwickler Board von Alchitry. Es verwendet den Xilinx Artix 7 FPGA der von den aktuellen Xilinx's Werkzeugen unterstützt wird.

- Artix 7 XC7A35T-1C - 33,280 logic cells

- 256MB DDR3 RAM

- 102 IO pins (3.3V logic level, 20 of then can be switched to 1.8V for LVDS)

- 9 differential analog inputs (1 dedicated, 8 mixed with digital IO)

- USB C to configure and power the board

- 8 general purpose LEDs

- 1 button (typically used as a reset)

- 100 MHz on-board clock (can be multiplied internally by the FPGA)

- Powered with 5V through USB C port, 0.1" holes, or headers

- USB to serial interface for data transfer (up to 12Mbaud)

- Dimensions of 65mm x 45mm