MMU: Unterschied zwischen den Versionen

Tw (Diskussion | Beiträge) (→Adressdekoder) |

Tw (Diskussion | Beiträge) (→Adressdekoder) |

||

| Zeile 140: | Zeile 140: | ||

Der CPLD erzeugt auch die Signale für das BM Mainboard: /RD, /WRT, ROM | Der CPLD erzeugt auch die Signale für das BM Mainboard: /RD, /WRT, ROM | ||

| − | Wenn die MMU adressiert wird, dann sind /RD und /WT auf high, das BM Mainboard ist inaktiv. Ansonsten wird R/W umgesetzt auf | + | Wenn die MMU adressiert wird, dann sind /RD und /WT auf high, das BM Mainboard ist inaktiv. Ansonsten wird R/W umgesetzt auf die Signale /RD und /WRT für das BM Mainboard. |

| + | |||

| + | Im Falle einer Zugriffsverletzung wird der externe Speicher nicht zugegriffen. Es erfolgt keine Selektion des externen Speicher über /RD und /WRT. Erfolgt die Zugriffsverletzung beim Fetch (Execute Access), dann wird ein NMI ausgelöst. Das OS muss diese Zugriffsverletzung dann entsprechend behandeln. | ||

Version vom 10. Juni 2022, 15:17 Uhr

Inhaltsverzeichnis

MMU - Memory Management Unit

Eine MMU verwaltet den Verfügbaren Arbeitsspeicher eines Computer System. Im Falle einer 8 Bit CPU, die einen sehr eingeschränkten Adressraum hat, wird durch den Einsatz einer MMU der Adressraum stark erweitert. Der Adressraum einer Motorola 6809 CPU ist auf 64K beschränkt, man spricht vom logischen Adressraum. Die MMU hingegen hat einen viel größeren Adressraum von mehreren MB, das bezeichnet man als physischen Adressraum.

Für die Motorola 6809 gibt es einen passenden Chip, die Motorola MMU 6829. Die 6829 sind jedoch heutzutage kaum noch erhältlich. Ziel dieses Projekt ist es, einen 6829 zu ersetzen mit heute noch gut erhältlichen Bauteilen.

Motorola MMU 6829

Die Idee hinter der MMU ist es, den logischen Adressraum der CPU in kleine Blöcke zu teilen. Jeder Block kann dann irgendwo im physischen Adressraum verschoben werden. Damit steht der gesamte physikalische Adressraum im Zugriff der CPU, natürlich nur Stückweise.

Je kleiner die Größe eines Blocks gewählt wird, desto flexibler kann die Sicht auf den physikalische Adressraum gestaltet werden. Allerdings vergrößert sich der Verwaltungsaufwand, je kleiner die Blockgröße gewählt wird. Im Falle der MMU 6829 ist die Blockgröße exakt 2K, damit hat man 32 Blöcke im logischen Adressraum der CPU.

Bei der MMU 6829 wird der logische Adressraum erweitert von 64K (16 Bit) auf 2MB (21 Bit). Umgesetzt wird das mit einem sehr schnellen SRAM. Dazu werden die obersten 5 Bit der logischen Adresse (LA11 bis LA15) als Adresse für ein 10 Bit SRAM verwendet (RA0 bis RA4). Die 10 Bit Daten im RAM bilden die obersten Bits der physischen Adresse (PA11 bis PA20).

MMU aus SRAM und CPLD

Das Ziel ist die Entwicklung einer eigenen MMU, die weitgehend kompatibel zur Motorola 6829 ist.

Die Umsetzung von logischer zu physikalischer Adresse erfolgt also über ein schnelles SRAM. Das SRAM sollte bei einer 3MHz CPU mindestens 12nS Zugriffszeit haben. Besser sind 10nS um auf der sicheren Seite zu sein.

Übliche SRAM mit 10nS Zugriff haben eine Datenbreite von 8 Bit. Also benötigen wir zwei dieser SRAM Bausteine. Die übrigen 6 Bit kann man sinnvoll nutzen, um den physikalischen Adressraum noch weiter zu vergrößern und andere Dinge (Memory Flags).

Der SRAM übernimmt im Betrieb die Umsetzung von logischer zu physikalischer Adresse. Aber der SRAM muss ja irgendwie einen sinnvollen Inhalt bekommen. Die CPU muss daher den vollen Zugriff auf dieses Mapping SRAM haben. Da kommt der CPLD ins Spiel, der übernimmt die Aufgabe, die Funktionen der MMU zu steuern.

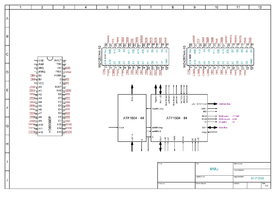

Die MMU-16 Hardware

Die MMU-16 braucht folgende Bauteile zur Funktion:

- SRAM zur Umsetzung von logischer auf physikalische Adresse

- CPLD zur Verwaltung der MMU

Das SRAM

Die Umsetzung von logischer auf physikalischer Adresse benötigt in der MMU 6829 exakt 10 Bit. Übliche SRAM Bausteine haben eine Datenbreite von 8 Bit. Also benötigen wir zwei dieser SRAM Bausteine. Die übrigen 6 Bit kann man sinnvoll nutzen, um den physikalischen Adressraum noch weiter zu vergrößern und andere Dinge zu ermöglichen (Memory Flags).

Einen Arbeitsspeicher von 2MB ist ausreichend für einen 8 Bit Computer. Andererseits ist Speicher heutzutage sehr preisgünstig zu haben, und man muss den möglichen Adressraum ja nicht vollständig nutzen. Daher werden 3 der übrigen Daten Bits benutzt, um den Adressraum von 2MB auf maximal 16MB zu erweitern.

Die übrigen drei Bits sind Flags, die besondere Dinge beim Zugriff auf den Arbeitsspeicher steuern. Sie steuern die Rechte auf den Speicherblock: lesen, schreiben, ausführen. Manchmal ist es sinnvoll, den Zugriff auf das RAM zu beschränken auf nur lesenden Zugriff (Ram als ROM verwenden). Genauso kann man auch den lesenden Zugriff beschränken. Die Ausführung von Code sollte vom OS beschränkt werden auf eigene Segmente, die nicht beschrieben werden können.

| Motorola 6829 | MMU-16 | |

|---|---|---|

| Blockgröße | 2K | 2K |

| Adressraum | 2MB | 16MB |

| Memory Flags | 0 | 3 |

| Anzahl Tasks | 4 | 256 |

Unsere MMU hat nun 32 Blöcke zu 2K im logischen Adressraum der CPU. Jeder Block kann im gesamten physischen Adressraum von 16MB bewegt werden (in 2K Schritte). Jeder Block hat drei Bit für die Zugriffsrechte.

Der physische Adressraum ist unterteilt in 8192 Seiten (2K * 8192 --> 16MB). Jeder der 32 Blöcke hat also eine Seiten Nummer (Page#). Die Seiten Nummer plus 3 Zugriffsbit benötigen insgesamt 16 Bit (2 mal 8 Bit --> 2 SRAM Bausteine je 8 Bit).

Die SRAM Bausteine haben 8K, 16K oder 32K. Alle drei Arten verwenden dasselbe Pinout und haben dieselbe PIN Belegung. Verwendet werden immer nur 8KB, deshalb kann man die RAM Art frei wählen, auch gemischt.

Die CPU sieht zu jedem Zeitpunkt immer nur 64KB (logischer Adressraum), also 32 Blöcke. Jeder Block liegt auf einer bestimmten Seite im physischen Adressraum. Diese 'Sicht' auf den physischen Speicher nennt man MAP (Memory MAP). Jede MAP wird beschrieben durch 32 Worte zu 16 Bit. In jedem der beiden SRAM Bausteine belegt eine Memory MAP exakt 32 Byte. Aus Sicht der CPU sind das 64 Bytes.

Ein SRAM mit 8KB kann 256 Memory MAPs speichern (32 * 256). Die Auswahl der MAP erfolgt über die Task# Nummer. Die Task# Nummer geht von 0 bis 255. Die Task# Nummern 0 und 1 haben besondere Bedeutung: Task#0 ist der System Task mit besonderer Zugriffs Berechtigung. Der Task#1 ist reserviert für DMA Zugriffe. Task# 2 bis 255 sind Benutzer Tasks. Die aktive Task# Nummer entspricht den Adressleitungen RA5 bis RA12 der SRAM Bausteine.

Warum braucht man mehrere Memory MAPs? Das braucht man dann, wenn man mehrere Programme gleichzeitig ausführen möchte, oder wenn man OS (System Task) und das Benutzer Programm trennen möchte. Hätte die MMU nur eine MAP, so müsste man bei jedem Task Wechsel alle 64 Byte umschreiben. So genügt ein Schreib Zugriff, die Task# Nummer.

Ein gutes OS trennt die Memory MAP der Benutzer Programme gegeneinander und von der eigenen Memory MAP. Dadurch bleibt das System stabil, auch wenn ein Programm 'abstürzt'. Jedes Benutzerprogramm ist in seiner eigenen 64K Welt gefangen und kommt nicht heraus. Böswilliger Schadcode kann den Speicher nicht verwüsten, er kann nur in der eigenen Speicher MAP Änderungen vornehmen. Der Zugriff auf Ressourcen kann vom OS verwaltet werden oder einem bestimmten Task zugeordnet werden. Dadurch ist alles gesteuert und geordnet, es entsteht kein Chaos durch Zugriff gleichzeitig von mehreren Tasks.

Der CPLD

Die Umsetzung von logischer Adresse (16 Bit) zu physikalischer Adresse (24 Bit) wird vom Mapping RAM übernommen. Der CPLD ist daran nicht beteiligt.

Der CPLD hat folgende Aufgaben:

- Bereitstellung von Register zur Steuerung der MMU

- Schreibzugriff auf den Inhalt des Mapping RAM

- Adressdekodierung für MMU Fenster

- Adressdekodierung für externe Speicher und IO

- Task# Verwaltung

MMU Register

Die Funktionen der MMU werden über die MMU Register gesteuert. Die Register sind weitgehend kompatibel zur Motorola MMU 6829, sodass ein Umstieg sehr einfach durchgeführt werden kann.

Die MMU ist sichtbar für die CPU in einem MMU Speicherfenster. Das MMU Fenster hat eine Größe von 128 Byte. Normalerweise liegt das Fenster an der logischen Adresse $FF00 bis $FF7F. Aber es kann prinzipiell auch an eine andere Adresse verschoben werden.

Das MMU Fenster ist nur sichtbar für den Task# 0 (Systemtask). Alle anderen Tasks sehen die MMU nicht, es kann auch nicht Mapping eingeblendet werden. Daher haben alle Benutzer Tasks und auch das DMA Zugriff auf die gesamten 64KB logischen Adressraum. Es geht kein Byte verloren durch MMU oder IO.

Der System Task sieht das MMU Fenster immer an seiner logischen Adresse, diese 128 Byte können nicht ausgeblendet werden.

Mapping RAM

Adressdekoder

Der CPLD erzeugt auch die Signale für das BM Mainboard: /RD, /WRT, ROM

Wenn die MMU adressiert wird, dann sind /RD und /WT auf high, das BM Mainboard ist inaktiv. Ansonsten wird R/W umgesetzt auf die Signale /RD und /WRT für das BM Mainboard.

Im Falle einer Zugriffsverletzung wird der externe Speicher nicht zugegriffen. Es erfolgt keine Selektion des externen Speicher über /RD und /WRT. Erfolgt die Zugriffsverletzung beim Fetch (Execute Access), dann wird ein NMI ausgelöst. Das OS muss diese Zugriffsverletzung dann entsprechend behandeln.

Task# Verwaltung

Spezielle MMU Bits

Es gibt spezielle Bits in der MMU, auf die man keinen direkten Einfluss hat:

- Reset Bit

- Das System Bit (Task# 0)

Das Reset Bit wird gesetzt, wenn die Reset Leitung auf Low gezogen wird. Die MMU läuft nun in einem speziellen Reset Modus:

- Physikalische Adressen A11 bis A23 sind immer high

- Das System Bit ist automatisch aktiviert

Die physikalische Adressbits der MMU sind alle high. Das bedeutet der Adressraum ist auch 2KB beschränkt, und zwar auf die oberste Page (Page# 8191). Also auf die höchste physikalische Adresse die es gibt. Dort MUSS ein ROM sein, denn die CPU führt als erstes ein Fetch aus auf den Reset Vektor. Der Reset Code muss ebenfalls in den obersten 2KB liegen, denn es sind ja nur die obersten 2KB sichtbar für die CPU.

Das MMU Fenster ist sichtbar, denn die MMU ist im System Modus (Task# 0). Daher darf der Reset Code nicht in dem Adressen Bereich liegen, wo das MMU Fenster liegt.

Achtung: Da die oberste Page ein ROM sein muss, hat die CPU nach dem Reset kein RAM zur Verfügung! Daher dürfen keine CPU Befehle ausgeführt werden, die RAM benötigen!

Der Reset Modus wird beendet, sobald die CPU das operative Task# Register (OPKEY) beschreibt. Daher muss unbedingt die Memory MAP für Task# 0 konfiguriert werden, bevor man das Register OPKEY beschreibt!

Das System Bit wird gesetzt, wenn ein Interrupt ausgelöst wird (IRQ, FIRQ, NMI, SWIx). Die MMU läuft nun im System Modus (Task# 0):

- Der operative Task wird auf 0 gestellt (System Task), unabhängig davon, was im OPKEY Register steht

- Das System Bit wird automatisch aktiviert

Die Memory MAP des System Task ist aktiv, wodurch automatisch die Interrupt Vektoren aus der System MAP gelesen werden. Die CPU führt den entsprechenden Code in der System MAP aus. Die Umschaltung zur System MAP erfolgt NACHDEM die CPU die Rücksprungadresse und die Register auf den Stack gelegt hat. Diese Daten befinden sich also auf dem Stack in der MAP des Benutzer Task.

Der System Modus wird beendet, indem man das FUSE Register beschreibt. Das FUSE Register ist ein 3 Bit Register, das als Zähler (Countdown) implementiert ist. Es zählt System Takte. Wenn der Countdown Zähler null erreicht, dann schaltet die MMU auf den eingestellten operativen Task# (im Register OKKEY).

Die Benutzung der MMU

Memory MAP

Inbetriebnahme

Das Betriebssystem

Zum Einsatz kommt NitrOS9 Level II. Die Basis dafür ist der Quellcode des NitrOS9 für den Tandy CoCo-III. Das NitrOS9 wird angepasst auf die im vorigen Kapitel beschriebene Hardware Plattform (NitrOS9 SBC).

Start Sequenz

Nach einem Reset fetched die CPU den RESET Vektor von der logischen Adresse $FFFE und führt den Code aus. Die MMU ist nach einem RESET in einem speziellen Modus. Die Adressleitungen PA11 bis PA23 sind high, daher wird der Reset Vektor gelesen von der physischen Adresse $FFFFFE in der obersten Page (Page 8191). Es läuft privilegierter Code, die MMU Konfig Register sind sichtbar an der Adresse $FF00 bis $FF7F.

Das erste was die CPU nun zu tun hat, ist die Konfiguration der MMU. Sonst hat man keinen Zugriff außerhalb der Page 8191. Die MMU bekommt nun die Konfiguration unter der NitrOS9 laufen kann. Dann wird der Kern Code gestartet. Je nach Art des NitrOS9 ist entweder das gesamte OS im ROM (20K) oder nur der Kern (4K).

News

- 09.06.2022 --

Downloads