Tools/LogicSniffer: Unterschied zwischen den Versionen

< Tools

Tw (Diskussion | Beiträge) (Die Seite wurde neu angelegt: „right|thumb|200px|Logic Sniffer right|thumb|200px|Logic Sniffer __TOC__<br /> == Logic Sniff…“) |

Tw (Diskussion | Beiträge) (→Spezifikation) |

||

| (4 dazwischenliegende Versionen desselben Benutzers werden nicht angezeigt) | |||

| Zeile 1: | Zeile 1: | ||

| + | [[Bild:LogicSniffer-top-02a.jpg|right|thumb|200px|Logic Sniffer]] | ||

[[Bild:LogicSniffer-top-01.jpg|right|thumb|200px|Logic Sniffer]] | [[Bild:LogicSniffer-top-01.jpg|right|thumb|200px|Logic Sniffer]] | ||

| − | |||

__TOC__<br /> | __TOC__<br /> | ||

== Logic Sniffer == | == Logic Sniffer == | ||

| Zeile 10: | Zeile 10: | ||

* 16 Kanäle mit bis zu 200MHz Sampling Rate | * 16 Kanäle mit bis zu 200MHz Sampling Rate | ||

* 32 Kanäle mit bis zu 100MHz Sampling Rate | * 32 Kanäle mit bis zu 100MHz Sampling Rate | ||

| + | * 16 Kanäle gebuffert und 5 Volt tolerant | ||

* Status Analyse mit bis zu 50MHz externen Takt | * Status Analyse mit bis zu 50MHz externen Takt | ||

* 256K Sample Speicher | * 256K Sample Speicher | ||

| Zeile 15: | Zeile 16: | ||

* Komplexe serielle und parallele Trigger | * Komplexe serielle und parallele Trigger | ||

* USB Anschluss (EIA232/RS232 - USB zu seriell Adapter) | * USB Anschluss (EIA232/RS232 - USB zu seriell Adapter) | ||

| + | * Stromversorgung vom USB | ||

| + | * alle Updates können über USB eingespielt werden | ||

* Java basierte Software für die Anzeige der Daten am PC | * Java basierte Software für die Anzeige der Daten am PC | ||

* I2C & SPI Protokoll Analyse | * I2C & SPI Protokoll Analyse | ||

| + | |||

| + | |||

| + | <gallery mode="traditional" widths=90px heights=90px perrow=9 caption=""> | ||

| + | Sump-dataii.png | ||

| + | La block diagram ver1-490.png | ||

| + | 800px-Cct-fpga-490.png | ||

| + | LA Buffer-dia.jpg | ||

| + | </gallery> | ||

<br /> | <br /> | ||

| + | |||

===== WEB Links ===== | ===== WEB Links ===== | ||

* [http://dangerousprototypes.com/docs/Open_Bench_Logic_Sniffer Logic Sniffer Wiki] | * [http://dangerousprototypes.com/docs/Open_Bench_Logic_Sniffer Logic Sniffer Wiki] | ||

* [https://www.sump.org/projects/analyzer/ SUMP Logic Aanalyzer] | * [https://www.sump.org/projects/analyzer/ SUMP Logic Aanalyzer] | ||

Aktuelle Version vom 13. Oktober 2019, 00:20 Uhr

Inhaltsverzeichnis

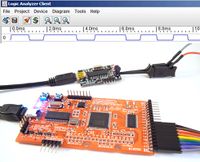

Logic Sniffer

Der Open Bench Logic Sniffer von Dangerous Prototypes ist ein Logic Analyzer mit 32 Eingänge. Die ersten 16 Eingänge sind 5V tolerant, die zweiten 16 Eingänge sind auf dem Wing Header heraus geführt. Mit dem Board kann man logische Signale analysieren, die . Das Board arbeitet mit der Software des SUMP Logic Aanalyzer.

Spezifikation

- 16 Kanäle mit bis zu 200MHz Sampling Rate

- 32 Kanäle mit bis zu 100MHz Sampling Rate

- 16 Kanäle gebuffert und 5 Volt tolerant

- Status Analyse mit bis zu 50MHz externen Takt

- 256K Sample Speicher

- Störfilter

- Komplexe serielle und parallele Trigger

- USB Anschluss (EIA232/RS232 - USB zu seriell Adapter)

- Stromversorgung vom USB

- alle Updates können über USB eingespielt werden

- Java basierte Software für die Anzeige der Daten am PC

- I2C & SPI Protokoll Analyse