FPGA/Open3S500E: Unterschied zwischen den Versionen

Tw (Diskussion | Beiträge) (→Beschreibung des DVK600 mit dem Core Board) |

Tw (Diskussion | Beiträge) (→Beschreibung des DVK600 mit dem Core Board) |

||

| Zeile 57: | Zeile 57: | ||

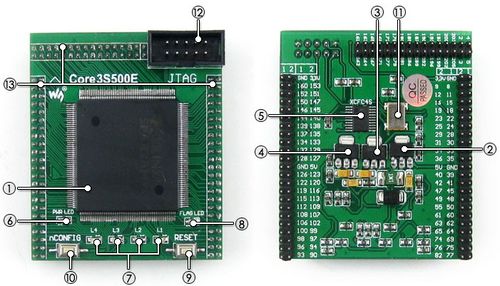

[[File:Core3S500E-intro.jpg|500px|Open3S500E]] | [[File:Core3S500E-intro.jpg|500px|Open3S500E]] | ||

| − | # XC3S500E: | + | # XC3S500E: XILINX Spartan-3E FPGA |

| − | |||

#* Operating Frequency: 50MHz | #* Operating Frequency: 50MHz | ||

| − | #* Operating Voltage: 1. | + | #* Operating Voltage: 1.15V~3.3V |

| − | #* Package: | + | #* Package: QFP208 |

#* I/Os: 116 | #* I/Os: 116 | ||

| − | #* LEs: | + | #* LEs: 500K |

| − | #* Debugging/Programming: JTAG | + | #* RAM: 360kb |

| − | # AMS1117-3.3 | + | #* DCMs: 4 |

| − | # | + | #* Debugging/Programming: supports JTAG |

| + | # AMS1117-3.3, 3.3V voltage regulator | ||

| + | # AMS1117-2.5, 2.5V voltage regulator | ||

| + | # AMS1117-1.2, 1.2V voltage regulator | ||

| + | # XCF04S, onboard serial FLASH memory, for storing code | ||

# Power indicator | # Power indicator | ||

| − | # LEDs | + | # LEDs |

| − | # | + | # FPGA initialization indicator |

# Reset button | # Reset button | ||

| − | # | + | # nCONFIG button: for re-configuring the FPGA chip, the equivalent of power reseting |

| − | + | # 50M active crystal oscillator | |

| − | + | # JTAG interface: for debugging/programming | |

| − | + | # FPGA pins expander, VCC, GND and all the I/O ports are accessible on expansion connectors for further expansion | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<br /> | <br /> | ||

Version vom 24. September 2019, 15:46 Uhr

Inhaltsverzeichnis

Das ist ein sehr gut dokumentiertes FPGA Entwickler Board der Firma WaveShare mit ausgezeichnetem Support. Dieses Board hat einen FPGA der Firma XILINX (XC3S500E) und es wird mit zahlreichem Zubehör geliefert.

Wie bei WaveShare üblich ist alles sehr modular aufgebaut. Es gibt verschiedene Core Module von XILINX und Altera, die auf WaveShare standardisierte "Mother Boards" gesteckt werden.

An den Motherboards können zahlreiche Erweiterungen gesteckt werden, sodass man diese Entwicklungsumgebung sehr flexibel gestalten kann.

Core Board 3S500E

Das Core Board enthält den FPGA und die notwendige Mindestbeschaltung. Es gibt unterschiedliche Core Boards von verschiedenen Hersteller (XILINX und Altera).

Mother Board DVK600

Das Motherboard verbindet das Core Board mit den zahlreichen Zusatz Modulen.

Zusatz Module

Die Zusatz Module werden einfach an das Motherboard gesteckt und sind so mit dem Core Board verbunden. Je nach Projekt verwendet man die gewünschten Module und steckt sich so einfach sein Gesamtsystem zusammen.

Beschreibung des DVK600 mit dem Core Board

- XC3S500E: XILINX Spartan-3E FPGA

- Operating Frequency: 50MHz

- Operating Voltage: 1.15V~3.3V

- Package: QFP208

- I/Os: 116

- LEs: 500K

- RAM: 360kb

- DCMs: 4

- Debugging/Programming: supports JTAG

- AMS1117-3.3, 3.3V voltage regulator

- AMS1117-2.5, 2.5V voltage regulator

- AMS1117-1.2, 1.2V voltage regulator

- XCF04S, onboard serial FLASH memory, for storing code

- Power indicator

- LEDs

- FPGA initialization indicator

- Reset button

- nCONFIG button: for re-configuring the FPGA chip, the equivalent of power reseting

- 50M active crystal oscillator

- JTAG interface: for debugging/programming

- FPGA pins expander, VCC, GND and all the I/O ports are accessible on expansion connectors for further expansion

Dokumentation